基于vivado(语言Verilog)的FPGA学习(2) |

您所在的位置:网站首页 › usb host device切换 › 基于vivado(语言Verilog)的FPGA学习(2) |

基于vivado(语言Verilog)的FPGA学习(2)

|

基于vivado(语言Verilog)的FPGA学习(2)——zedboard开机测试和程序烧写

终于找到之前写的部分了,在OneNote上,以后还是专注写在一个地方 1. 系统架构图

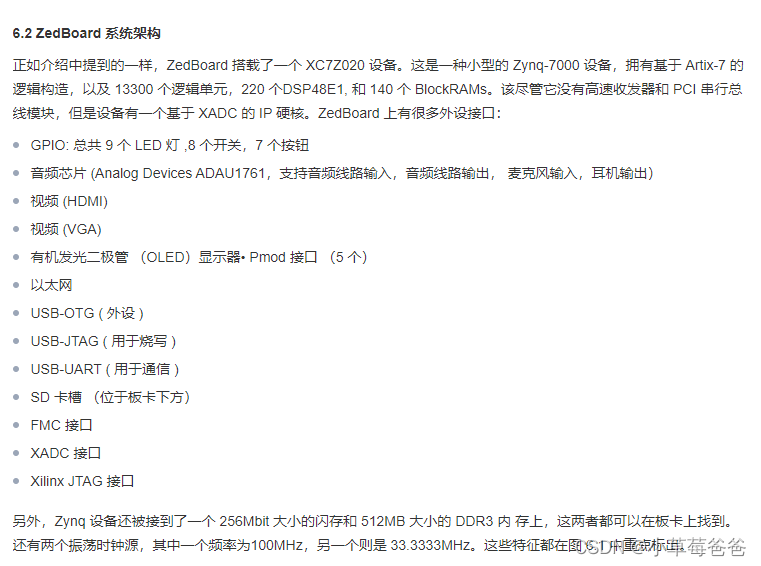

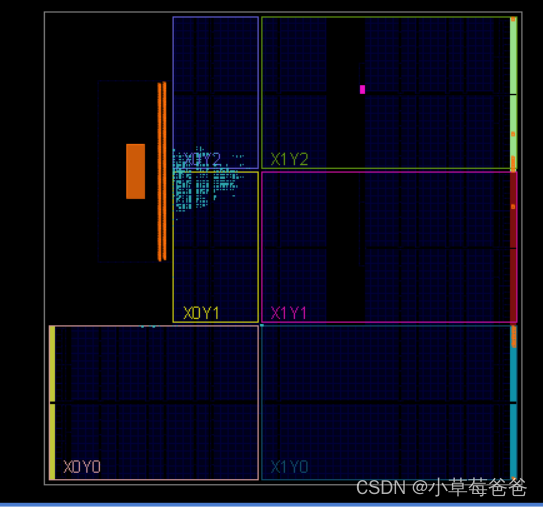

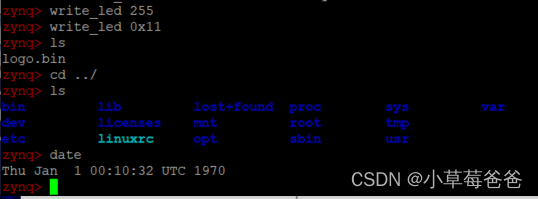

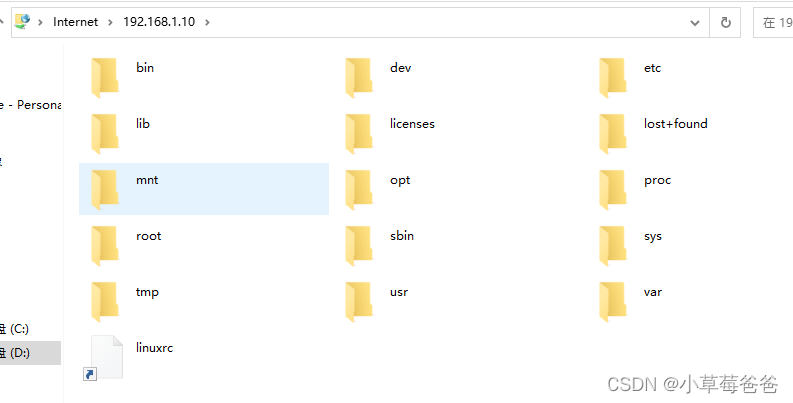

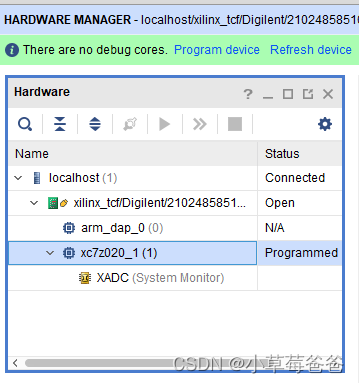

ZedBoard 可以通过四个不同的方法烧写,这些方法是: USB-JTAG 这是默认的并且是最直接的烧写 ZedBoard 的方法 , 这只要通过 ZedBoard 工具包的 USB 到 micro-USB 连接线就可以直接完成。 传统 JTAG 板卡上有一个可用的 Xilinx JTAG 接口,如果需要的话可用来 替代 USB-JTAG 连接。这会需要一根未包含在 ZedBoard 工具包中的连接线:如一根 Xilinx Platform USB 连接线 [11],或者一根 Digilent USB-JTAG 烧写线 [10]。 Quad-SPI 闪存 板卡上的闪存是非易失性的,因此它可以用来保存板卡上 次断电时的配置信息。使用这种方法不需要连接线来烧写 Zynq 设备。 SD 卡 ZedBoard 的背面有一个 SD 卡槽。利用这个特性可以通过 SD 卡中存 储的文件来烧写 Zynq,并且不需要任何烧写线。这种方法在 《ZedBoardGetting Started Guide》中有所描述 [6]。 ZedBoard 的用户可以通过一系列的跳线来选择引导 / 烧写方式,这些跳线位于 Digilent logo 的下方,并在图 6.4 中有所标注。在五个跳线中,中间的三个被用 来定义板卡的烧写信息来源 (JTAG,闪存或 SD 卡),最右边的控制 JTAG 的模式,最左边则决定内部 PLL 是否被使用。 上文引用网址 这一个上一小节也提供,单二者用的不是一个例子 操作目录如做所示。 第一个是项目管理(project manager),其中右基础设置、添加头文件(例如约束文件或者源代码文件)、语言模板(相当于语言帮助,里面有些常用句模板、IP目录 第二个是IP 综合块,里面右创建、打开和产生block design 第三个是仿真(可以看,里面有五种不同的仿真模式(行为仿真、综合功能仿真、综合时序仿真、实现功能仿真、实现时序仿真) 第四个是RTL分析(寄存器级别),查看当前设计的基础原理图 第五个是综合分析(synthesis),查看当前元器件级别的原理图 第六个implementation,实现级别,查看在当前硬件上的原件占用以及排布情况 (一块块的,酷似农田) 第七个是程序和debug,其中第一个是产生bitestream文件,这类文件适用于烧写至硬件中执行。但事先需要打开目标硬件,在右击当前硬件选择program device,即可烧写bit流文件至zedboard中 3. USB转串口测试收到的板子在SD卡内预装了LINUX内核和文件系统,下面就是给大家介绍如何使用串口终端查看启动过程的输出,以及使用简单命令控制读开关量和写数码管; 连接以太网线实现了HTTP协议可以通过网页访问板子的WEB页面,通过SSH客户端可以对板子进行控制; 连接HDMI之后在屏幕上显示了两只企鹅(证明HDMI正常);连接VGA显示;在OLED上显示DIGILENT的图标。 首先需要拷贝SD_IMAGE内的文件到SD卡的跟目录下。 3.1.串口:先连接串口,打开putty_V0.63.0.0.43510830软件,连接主机和zedboard(需要安装USB转串口的驱动)(如下图CP210xVCPInstaller_x64) 就可以用putty_V0.63.0.0.43510830软件输入查看灯情况和开关情况等 搜索ip文件可以看见Linux目录 输入:ftp://192.168.1.10/ 第一步:用vivado生成源代码文件和约束文件 第二步:调试成功后,生成bits流文件 第三步:open target连接zedboard: 上图中,arm是32arm:ps-》programmable system 处理器系统 xc7z020_1: pl-》 programmable logic 这次用的就是pl,就是将ZYNQ7当做一个单纯的FPGA来使用。 第四步:右击选择program device,即可烧写bit流文件至zedboard中 5.PS处理器系统Zynq7这块板子内核分为ps和pl,其中,pl表示处理器可编辑器件,单独使用可以看作FPGA,ps是处理器系统,例如arm32这样的嵌入式cpu,与pl不同的是:语言一般使用c、c++这样的软件开发语言。本次尝试就是使用ps实现一些串口功能。 PS: programmable system 这部分上学期写的,这学期好久没看都有点忘记了,所以要多实践!

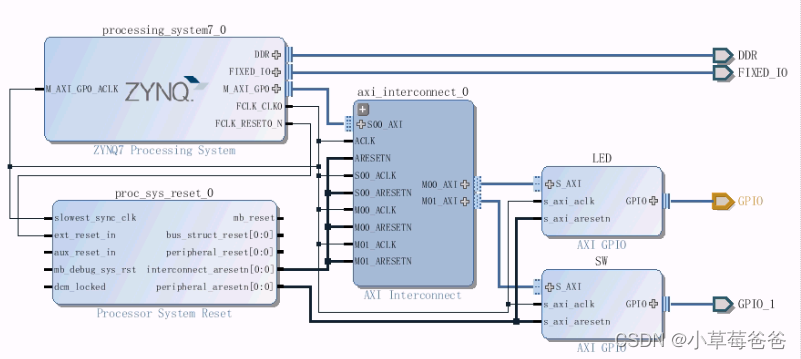

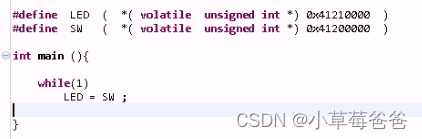

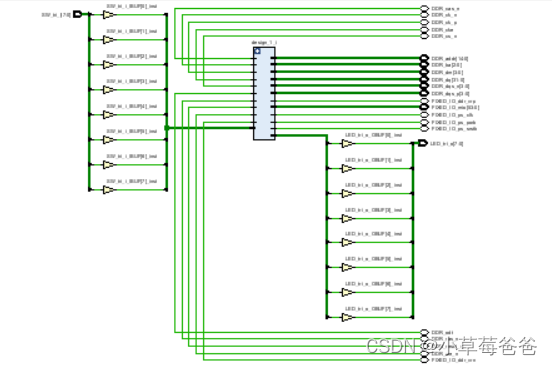

ZYNQ7的逻辑部分PL和处理器PS部分采集协同工作才能体现出其强大。这个例子只是简单的是一个实现:将FPGA当做一个PS处理器的外设,通过寄存器地址映射到PS的寻址空间。在处理器的使用C程序访问这些寄存器,来实现软件和逻辑结合的协同设计的效果。具体步骤就是先在VIVADO配置ZYNQ处理器吗,做好FPGA的外设,互联完成之后生产BIT流文件下载到板子。在SDK环境下开发好软件之后,进行在线调试运行。下面展示VIVADO的操作步骤,以及SDK的下对代码进行分析 步骤: 1、 创建项目、创建一个IP块设计(block design),在块中加入ZYQN主模块、AXI interconnect交互模块、两个GPIO(一个led一个sw,8输入8输出)、一个reset模块 (这里我一开始生成五个模块后直接自动连接,后来运行时会报错,查看后发现有线连错了。所以自动连线一定要注意,尤其时reset的线) 2、和PS处理器系统一样吗,需要右击当前bd文件,先generate output product,再create HDL wrapper。产生硬件描述语言,并自动产生top文件。 3、编译通过后,生成bits流文件,再open target 4、expert hardware 再launch SDK, 5、打开SDK后,创建新的application project,再设置时,选择外设测试。在testperiph.c代码中选择适当的测试代码,其余注释掉 可以将主函数换成上述代码,这样LED和SW就作为arm的外设进行调试。 总结:左边的方法不知道好不好用,还是说直接用Verilog写到底更切合FPGA习惯。但是ZYNQ的优势也是在于结合PS和PL。目前学习和接触的实践太少了,仍需要进一步了解。 当时电脑同时安装了vivado和 vivado HLS,找了许多解释的: |

【本文地址】

今日新闻 |

推荐新闻 |

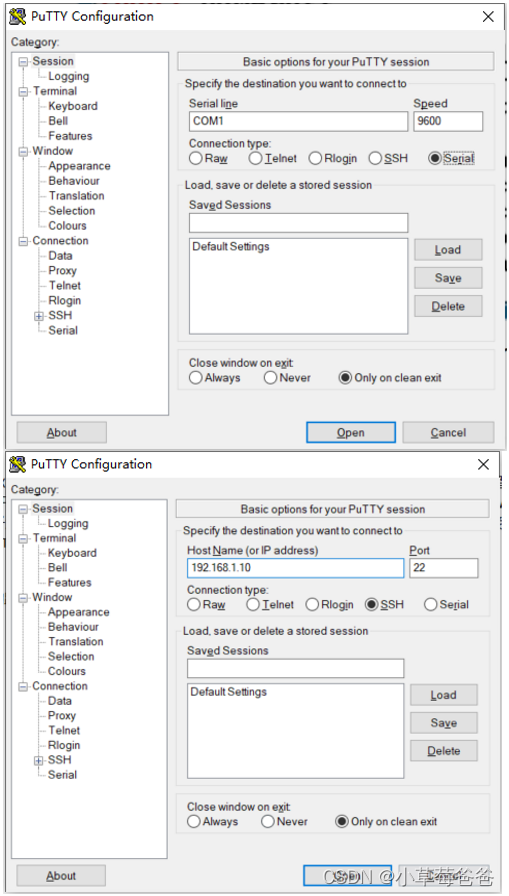

步骤: 跳线安装readme设置,可以只通过串口连接,也可以通过网口(下图左为串口,右为网口SSH)

步骤: 跳线安装readme设置,可以只通过串口连接,也可以通过网口(下图左为串口,右为网口SSH)

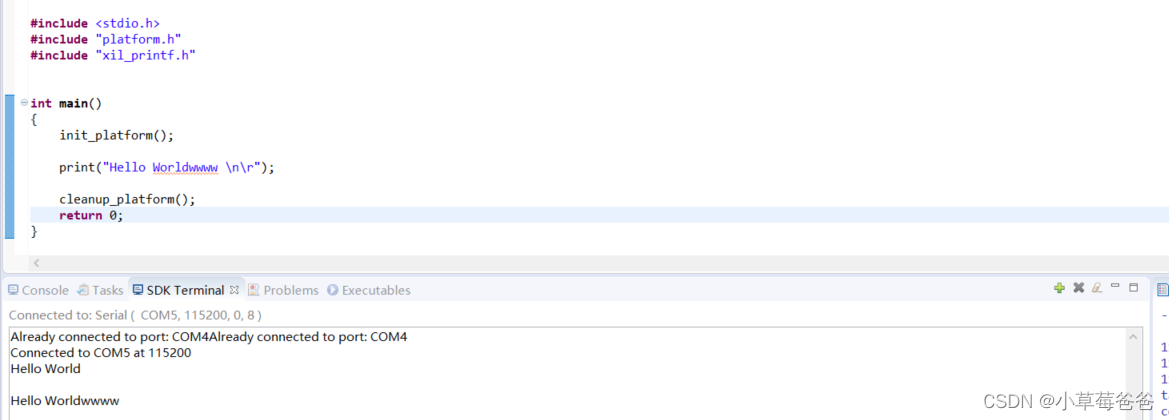

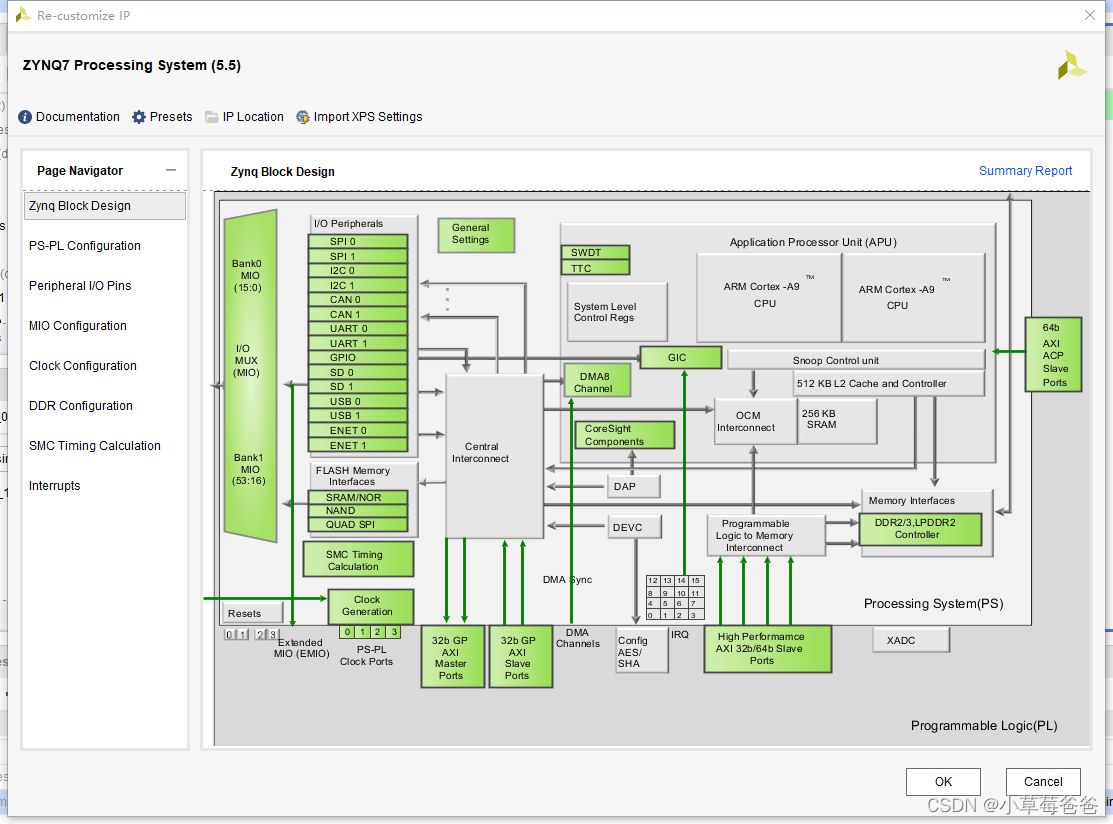

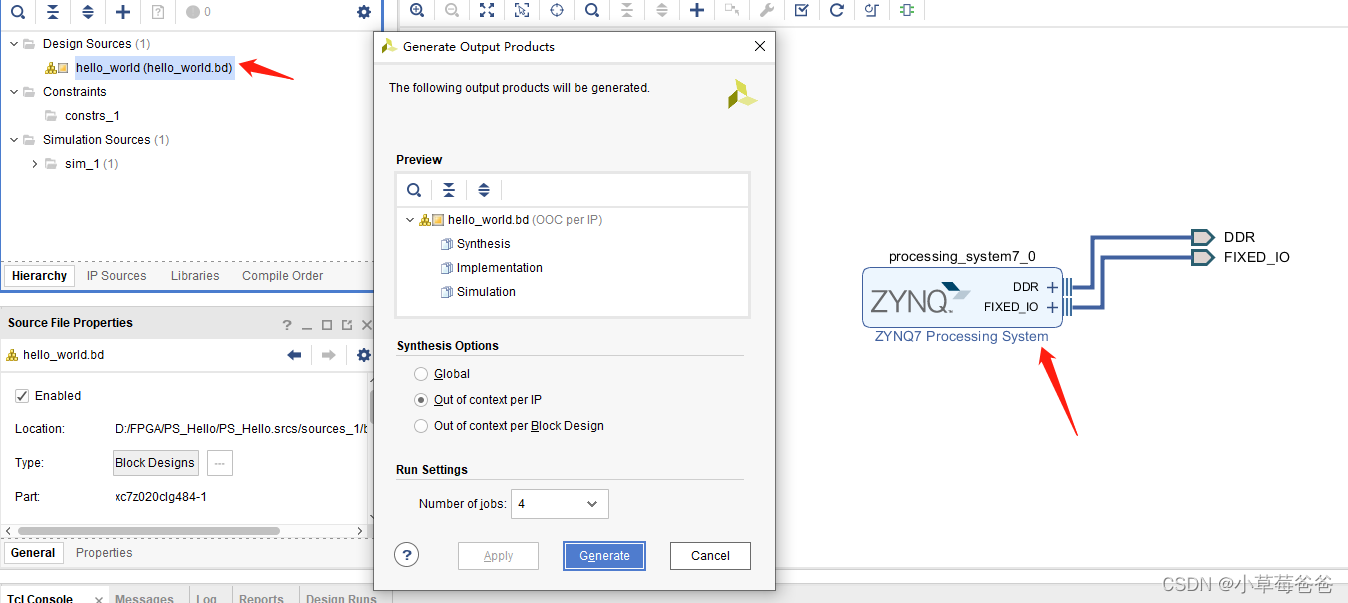

1. 点击生成某个bd文件,board design 设计IP

1. 点击生成某个bd文件,board design 设计IP  2. 双击PS产生左图。去掉不用的端口模块,以免重新连接

2. 双击PS产生左图。去掉不用的端口模块,以免重新连接  3. 右击bd文件,先generate output product,再create HDL wrapper。产生硬件描述语言,并自动产生top文件。 4. 生成bits流文件 5. 导入SDK,并自动打开SDK

3. 右击bd文件,先generate output product,再create HDL wrapper。产生硬件描述语言,并自动产生top文件。 4. 生成bits流文件 5. 导入SDK,并自动打开SDK  6. 打开串口(与烧写口不是一个口),运行程序

6. 打开串口(与烧写口不是一个口),运行程序